■ DSPに弄(もてあそ)ばれる自虐日記

■

(第2弾)

という訳で、懲りずに再びDSPと遊んでみようと思います。今回も弄(もてあそ)ばれるのは分かってますが、ドンキホーテとなる覚悟です。来年は還暦の60歳となるHYDの心意気だけは酌んで頂き、前へ進められるよう強く背中を押して下さいナ。

年末始に田舎に帰省して、親孝行やら初詣、雪降ろしをして横浜に帰って来た。すると年賀状に混じって、JASTAのJA1DSP田辺さんがブルガリアに製作依頼していた両面基板が届いていた。昨年の暮れに、近い内に送付する旨の連絡を受けていたのだが、実際に目の当たりにすると、やはりウレシイ。小さな基板上に、フィルタ選択用のDIP−SWやSPK−AMP、入出力コネクタまで配置されている。当たりの然で、ジャンパー線も不要で、ディジタル/アナログの電源ラインの分離もFBになっている。早速、製作したいところだが、モノには順番というものがある。先ずは製作途中のFRMSを先にやっつけよう。

足りない部品を出張の帰りに川崎のサトー電気で購入。パーツは全て揃ったので、ケースに罫書し穴開けなどケース加工の準備完了。

2010-01-06 FRMSケース加工終了

電源SW、BNCのコネクタ×2、D−Subコネクタ、電源ジャックの穴開けと何個かのビス穴開けを実施。ケースは薄いアルミ板なので、ヤスリ掛けを含めて簡単に終了。まだ寝る迄に時間があるので、コネクタ〜基板、電源〜SWなどの配線も始めた。いつもの寝る時間になったが、もう少し・もう少しと半田付けを進めて0時半に配線も終了。寝不足になるので、さすがに動作確認は明日ってコトに。

2010-01-08 FRMS動作確認

『明日は土曜で休み』というコトもあり、腰を落ち着けて(ウソ、『明日は休み』ということでシコタマ呑んだ後で)動作確認を実施。ヤッタネェー! という乾杯の準備をしていたのだが、PC上で立ち上げたFRMSのソフトが動かない。イロイロと動作条件を変えてみても同じである。ココで遅ればせながら電源電圧などを確認した、ヲイヲイ。どうやら電源電圧はOKのようなのでICチップ等は壊れていない筈である。となると、PCとの通信がNGなのでは、と一番怪しいトコロを確認。オシロで端子の波形を確認すると、何かおかしい。プラス・マイナスの両方に振れる信号なのに、マイナス側にしか振れていない。しかもTxdとRxdとが反対のような気がする。ここで回路図とニラメッコ。う〜ん、端子番号を完全に間違えている。Rxd・Txd・GNDの3本だけなのだが、全て間違えていた。こりゃ、ヒョッとするとAMD3202AのRS232CインタフェースICチップが壊れているかも。急いで配線をヤリ直し電源を入れると、PCのFRMSソフトが動き出し、ディスプレイに何やら表示をし始めた、ヤッタネェー!

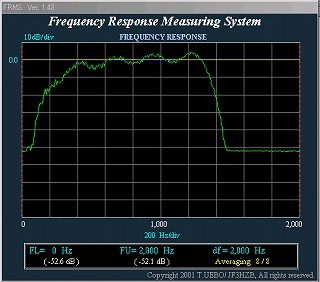

先ずは、以前に製作していたDSPによるLPFの特性を測定してみた。FRMSはRF帯を意識した作りになっており、1KHz以下でのAF帯では使用出来難いという情報もあった。しかし、カップリング・コンデンサを4.7μFと大きくしたためか、300Hz程度までは使えそうである。VuP用のLPFの特性は次のようになった。DSPの影響 or 測定系の影響で、ノイズフロアレベルが高いので−50dB以下は測定できない。でも必要にして十分な性能で、ニンマリ。当たりの然で、祝杯の缶チュウハイを立て続けに2本も空にしたが、物足りないモノだから芋焼酎も出して来て祝杯を重ねるのでした。

昨晩の酒が身体に残っていたので、先ずは床屋で頭を短く刈って貰い、頭がシャキィーッとなったところで原付スクーターで小机のサトー電気に買い物。さすがにDIP−SWと2Pコネクタ等はパーツ・ボックスに入っていなかったのである。僅かな部品でも、無いことには製作は進まない。その点、原付で30分も走るとパーツ屋が2箇所(エジソンプラザとサトー電気)もあるのはウレシイ。リタイアして田舎にQSYしたら、如何するのだろうかしらん。帰宅後、早速半田ごてを温っため、部品を取り付けていきます。部品配置のシルク印刷があるので、イトも簡単に終了。コネクタが多いが、今回はFRMSで測定したいこともあり、実際にコネクタを使用するのは電源ラインとLEDのみ。そうそうLM386−3NはMax+9Vなので、直流電源の+13.8Vを直接入れられない。このため+9Vの3端子レギュレータを一段カマスことにした。これでハード側の準備は終わり。

ソフトの方は以前のHexコードを<PICkit−2+ソケット・アダプタ>で焼付け。それにしても、これまで使用していたdsPICライタと比べると、このPICkit−2は、速いのなんのって驚くばかり。これまでのライタでも特にイライラすることはなかったけれど。で、新基板+DSP処理の動作をFRMSで測定し、問題なく動作することを確認した、ウレシヤ。

(新基板の方で、低域が少し下がっていますが、回路定数を変更して現在はフラットです)

<*「あっさぁー」は飛騨弁講座参照>

今日は『成人の日』なんだが、何だかナァー。というのも、1月15日が成人の日という思い込みが強くて、11日ではピィーンと来ない。ぢつは1月15日は私HYDの誕生日で、昔は祝日として国民の皆さんから祝って貰っていたのである Hi それはともかく、JASTAのOMさんからイロイロとDSPのソフトに関して指摘と知恵・工夫を頂いている。これを取り込むべく、ソースを変更して動作の確認をしようと、思ってソースの変更を実施した。この後、コンパイルしようとするが、何故かbuildできない。その代わりエラー表示がドドーッと吐き出される。エラー内容を見てもトンチンカンなものばかり。う〜ん、おかしい!。という訳で、以前にbuildがOKになったソースで試すも、同様にエラー表示が山ほど出て来る。ココでハタと気が付いた、これはMPLAB−IDE側の問題なのではないか、と。たぶん、どこかのファイルを壊したのではなかろうか。以前にも似たようなコトがあった。で、MPLABのVer.8.3を使用していたが、最新版のVer.8.4をダウンロード(何と、110MBと巨大)して、Ver−UPした。でも、時間が掛かった割りに結果は全く同じである。う〜ん、弱った・困った、どうしようかしらん。

2010-01-12 MPLAB修復

前にも同様な経験をしていた筈なので、メモを引っくり返して2008年10月28日に同様なトラブルに遭ったことが分かった。この時は「ライブラリーの中の必要なファイル容量が1つだけ0バイトになっていた」ということから、この原因を探して修復している。当時と同様に調べてみると、今回も0バイトのファイルがあった。Ver−UPに関係ないファイルだったようで、Ver−UPしても修復されないようである。しょうがなく、バックアップしていたドライブから、クダンのファイルをコピーしたところ無事に修復、やれウレシヤ。

エラー表示がされるとソースの該当箇所を見るが、ソースとは関係ないエラー表示の場合、Projectを構成するファイルの登録ミスの可能性が高い。しかし新規に作成したばかりのProjectでは、この構成ファイルにはスグには反映されず、アタカもファイルが無いような表示となる。ここでパニくってしまうと、登録済みにもかかわらず、再度上書きで登録してしまいゼロByteファイルになってしまうようである。今後、注意が必要である。

原因が分かり修復したところで、肝心のソースをコンパイルしてdsPICに焼付け新基板に装着した。いつもの「あっさぁー」をして電源を入れたが、「あっさぁー」の効果はなく動いてくれない、ガックリ。

【番外】長年使用していたヤニ入り半田が無くなった。スリ切れていて表示が読めないが、多分500gのモノではないかと思う。当初は使い切れるものか?と購入する際、真剣に悩んだモノである。たまたまオークションで少し使用した半田が出ていたので思わず「ポチッ」とした。電子秤で測ると、ピッタシ800gでズシリと重い。今度は死ぬまでには使い切れないだろうナァ、絶対に。

OMからのアドバイスを受けて、いろいろとソフトに機能を盛込んでみた。ようやくBuild出来る環境になったのだが、如何せん肝心のソフトの動作がNG。マトモに動いてくれない。動作確認の簡単な試験ソフトでは思惑通りに動くのだが、フィルタの種類を増やしたり、Resetせずにフィルタ切替えを行おうとすると、動作しないのである。アレコレとport関連やinterrupt関連をイジってみたが、全くNGである。ココで初心に戻り、動作している試験ソフトのソースと作成したソースとを微に細に入り、時間を掛けて比較してみた。すると、超単純な部分で漏れがあるのを発見!。これを修正しdsPICに焼き付けて動作させると、『ヤッタネェー』であった。イツモなら零時を回って寝ている時間なのだが、歓喜の乾杯をしてから布団の中に。

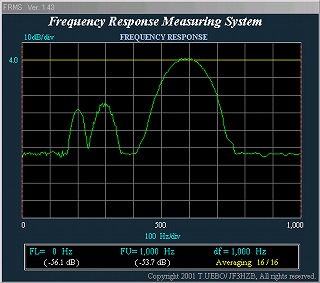

FRMSは便利な測定器である。測定する度にPCを立ち上げるのが面倒であるが、便利さを考えると面倒臭さも屁のようなもの。もっと早く製作しておけば良かった、と後悔シキリである。で、今日もコレでDSP処理によるCW用の新たに設計した100Hz幅の狭帯域BPFの周波数特性を測った。中心周波数やバンド幅など、設計通りなのだが、センターから離れた300Hz辺りに、妙なサイドローブが出ている。FIRの係数によっては、このローブが出ることもあるが、当然そんなバカな設計はしていない。500Hz幅までBPFの帯域が広がると、このサイドローブも目立たなくなる。う〜ん、何故だろう?